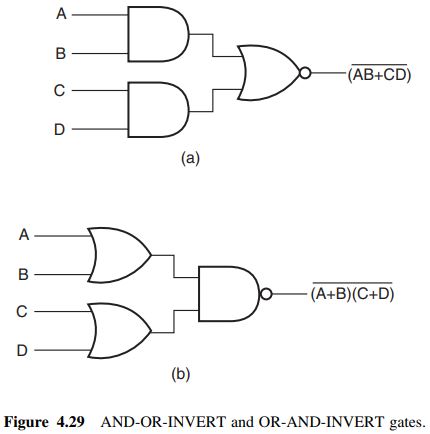

4.7 AND-OR-INVERT Gates

2. Alat dan Bahan

[Daftar]

2.2 Bahan

[Daftar]

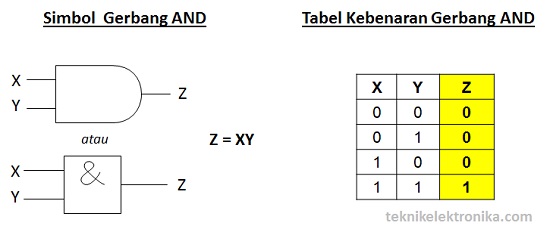

1. AND gate (IC 4081 dan 4082)

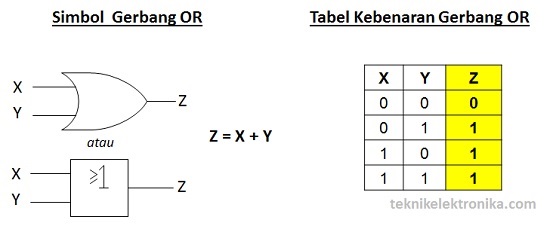

2. OR gate (IC 4071)

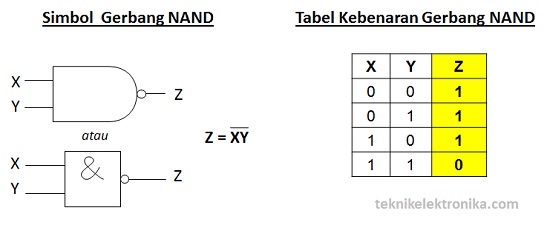

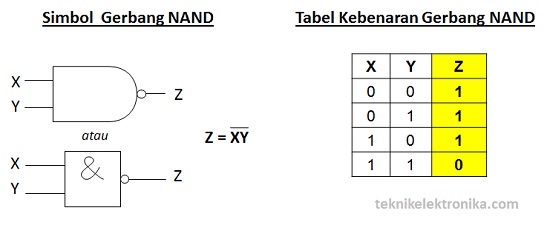

3. NAND gate (IC 4011)

4. NOR gate (IC 4001 dan 4002)

AND adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila salah satu, sebagian atau semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila semua inputnya berlogika 1.

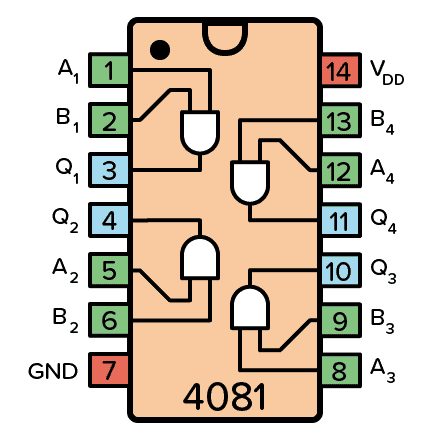

Konfigurasi Pin (4081):

Konfigurasi Pin (4082):

Fitur:

1. Medium-Speed Operation - tPHL = 60 ns at VDD = 10V

2. 100% tested for quiescent current at 20V

3. Maximum input current of 1uA at 18V over full package-temperature range; 100 nA at 18V and 25C

4. Noise margin (full package-temperature range) = 1V at VDD=5V, 2V at VDD=10V, 2.5V at VDD=15V

5. Standarized, symmetrical output chareacteristics

6. 5V, 10V, and 15V parametric ratings

Datasheet IC 4081 dan 4082

Konfigurasi Pin (4081):

Konfigurasi Pin (4082):

| Pin Number | Pin Name | Description |

|---|---|---|

| 1 & 13 | Q1 & Q2 | Output gate 1 dan 2 |

| 2, 3, 4, 5 | A1 - D1 | Input gate 1 |

| 12, 11, 10, 9 | A2 - D2 | Input gate 2 |

| 7 | GND | Ground |

| 14 | VDD | Input tegangan VDD |

Fitur:

1. Medium-Speed Operation - tPHL = 60 ns at VDD = 10V

2. 100% tested for quiescent current at 20V

3. Maximum input current of 1uA at 18V over full package-temperature range; 100 nA at 18V and 25C

4. Noise margin (full package-temperature range) = 1V at VDD=5V, 2V at VDD=10V, 2.5V at VDD=15V

5. Standarized, symmetrical output chareacteristics

6. 5V, 10V, and 15V parametric ratings

Datasheet IC 4081 dan 4082

2. OR gate (IC 4071)

OR adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila salah satu, sebagian atau semua inputnya berlogika 1.

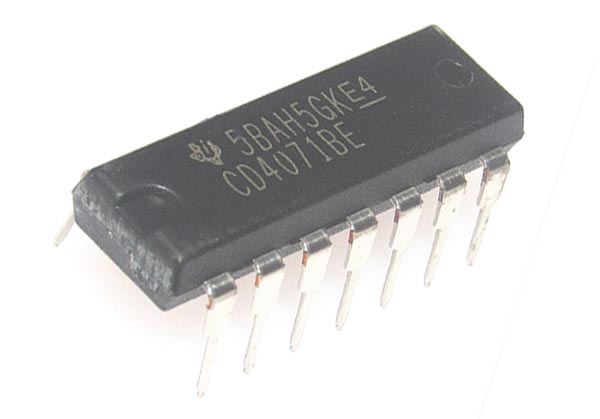

Konfigurasi Pin:

Fitur:

1. Dual Input OR Gate – Quad Package

2. Typical Operating Voltage: 5V

3. Operating Voltage Range: -0.5V to +20V

4. DC input current: ±10mA

5. Power Dissipation: 500mW

6. Minimum logic Low voltage @+5V: 1.5V

7. Minimum Logic High voltage @+5V: 3.5V

8. Propagation Delay @5V : 250ns (maximum)

9. Transition Time @5V :200ns (maximum)

Datasheet IC 4071

Konfigurasi Pin:

Fitur:

1. Dual Input OR Gate – Quad Package

2. Typical Operating Voltage: 5V

3. Operating Voltage Range: -0.5V to +20V

4. DC input current: ±10mA

5. Power Dissipation: 500mW

6. Minimum logic Low voltage @+5V: 1.5V

7. Minimum Logic High voltage @+5V: 3.5V

8. Propagation Delay @5V : 250ns (maximum)

9. Transition Time @5V :200ns (maximum)

Datasheet IC 4071

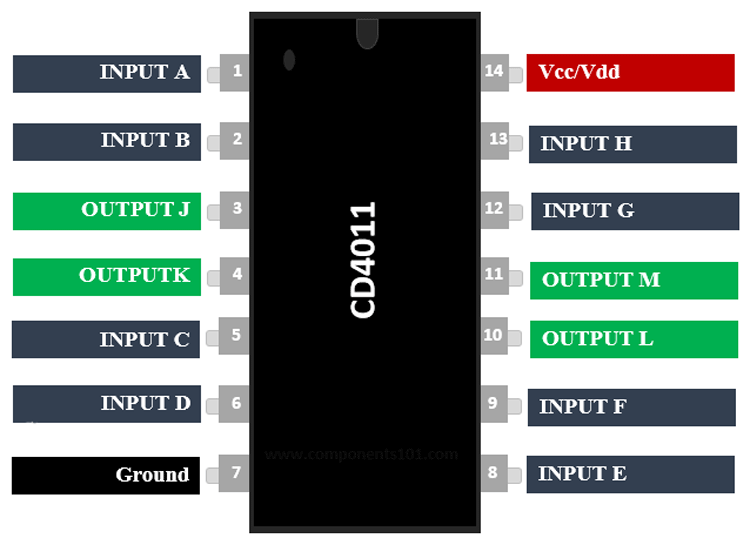

3. NAND gate (IC 4011)

NAND akan menghasilkan output berlogika 0 apabila semua inputnya berlogika 1 dan sebaliknya output berlogika 1 apabila salah satu, sebagian atau semua inputnya berlogika 0.

Konfigurasi Pin:

Fitur:

1. Dual Input NAND Gate – Quad Package

2. Typical Operating Voltage: 5V

3. High-Level Output Current:- 1.5 mA

4. Low-Level Output Current: 1.5mA

5. Propagation Delay Time:60 ns

6. Operating Temperature Range:- 55 C to + 125 C

Datasheet IC 4011

Konfigurasi Pin:

Fitur:

1. Dual Input NAND Gate – Quad Package

2. Typical Operating Voltage: 5V

3. High-Level Output Current:- 1.5 mA

4. Low-Level Output Current: 1.5mA

5. Propagation Delay Time:60 ns

6. Operating Temperature Range:- 55 C to + 125 C

Datasheet IC 4011

4. NOR gate (IC 4001 dan 4002)

NOR adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila salah satu, sebagian atau semua inputnya berlogika 1 dan sebaliknya output berlogika 1 apabila semua inputnya berlogika 0.

Konfigurasi Pin (4001):

Konfigurasi Pin (4002):

Fitur:

1. Propagation delay time = 60 ns at CL=50pF, VDD=10V

2. Buffered inputs and outputs

3. Standarized symetrical outputs characteristics

4. 100% tested for maximum quiescent current at 20V

5. 5V, 10V, and 15V parametric ratings

6. Maximum input current of 1uA at 18V over full package-temperature range; 100nA at 18V and 25C

7. Noise margin (full package-temperature range) : 1V at VDD=5V, 2V at VDD=10V, 2.5V at VDD=15V

Datasheet IC 4001 dan 4002

Konfigurasi Pin (4001):

Konfigurasi Pin (4002):

| Pin Number | Pin Name | Description |

|---|---|---|

| 1 & 13 | Q1 & Q2 | Output gate 1 dan 2 |

| 2, 3, 4, 5 | A1 - D1 | Input gate 1 |

| 12, 11, 10, 9 | A2 - D2 | Input gate 2 |

| 7 | GND | Ground |

| 14 | VDD | Input tegangan VDD |

Fitur:

1. Propagation delay time = 60 ns at CL=50pF, VDD=10V

2. Buffered inputs and outputs

3. Standarized symetrical outputs characteristics

4. 100% tested for maximum quiescent current at 20V

5. 5V, 10V, and 15V parametric ratings

6. Maximum input current of 1uA at 18V over full package-temperature range; 100nA at 18V and 25C

7. Noise margin (full package-temperature range) : 1V at VDD=5V, 2V at VDD=10V, 2.5V at VDD=15V

Datasheet IC 4001 dan 4002

3. Dasar Teori

[Daftar]

AND-OR-INVERT Gates

Gerbang AND-OR dan OR-AND dapat digunakan untuk mengimplementasikan ekspresi Boolean sum-of-products dan product-of-sums.

Simbol AND-OR-INVERT dan OR-AND-INVERT, dapat disebut two-wide, two-input. Disebut two-wide karena terdapat 2 gate sebagai input dan two-input karena pada setiap gate input terdapat 2 input.

Simbol two-wide, four-input AND-OR-INVERT. Disebut two-wide karena terdapat 2 gate sebagai input dan four-input karena pada setiap gate input terdapat 4 input.

Simbol four-wide, two-input AND-OR-INVERT. Disebut four-wide karena terdapat 4 gate sebagai input dan two-input karena pada setiap gate input terdapat 2 input.

Daftar IC AND-OR-INVERT gate:

1. 7451 Dual two-wide two-input three-input AND-OR-INVERT gate (TTL)

2. 7454 Four-wide two-input AND-OR-INVERT gate (TTL)

3. 7455 Two-wide four-input AND-OR-INVERT gate (TTL)

4. 4086B Four-wide two-input AND-OR-INVERT gate (CMOS)

5. 10117 Dual two-wide two- to three-input OR-AND/OR-AND-INVERT gate (ECL)

Gerbang AND, OR, NAND, dan NOR

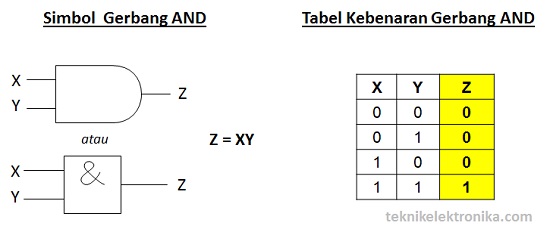

Gerbang AND

AND adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila salah satu, sebagian atau semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila semua inputnya berlogika 1.

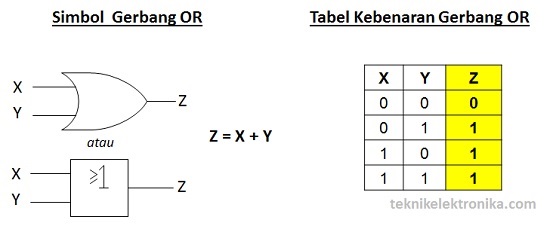

Gerbang OR

OR adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila salah satu, sebagian atau semua inputnya berlogika 1.

Gerbang NAND

NAND akan menghasilkan output berlogika 0 apabila semua inputnya berlogika 1 dan sebaliknya output berlogika 1 apabila salah satu, sebagian atau semua inputnya berlogika 0.

Gerbang NOR

NOR adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila salah satu, sebagian atau semua inputnya berlogika 1 dan sebaliknya output berlogika 1 apabila semua inputnya berlogika 0.

Gerbang AND-OR dan OR-AND dapat digunakan untuk mengimplementasikan ekspresi Boolean sum-of-products dan product-of-sums.

Simbol AND-OR-INVERT dan OR-AND-INVERT, dapat disebut two-wide, two-input. Disebut two-wide karena terdapat 2 gate sebagai input dan two-input karena pada setiap gate input terdapat 2 input.

Simbol two-wide, four-input AND-OR-INVERT. Disebut two-wide karena terdapat 2 gate sebagai input dan four-input karena pada setiap gate input terdapat 4 input.

Simbol four-wide, two-input AND-OR-INVERT. Disebut four-wide karena terdapat 4 gate sebagai input dan two-input karena pada setiap gate input terdapat 2 input.

Daftar IC AND-OR-INVERT gate:

1. 7451 Dual two-wide two-input three-input AND-OR-INVERT gate (TTL)

2. 7454 Four-wide two-input AND-OR-INVERT gate (TTL)

3. 7455 Two-wide four-input AND-OR-INVERT gate (TTL)

4. 4086B Four-wide two-input AND-OR-INVERT gate (CMOS)

5. 10117 Dual two-wide two- to three-input OR-AND/OR-AND-INVERT gate (ECL)

AND adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila salah satu, sebagian atau semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila semua inputnya berlogika 1.

Gerbang OR

OR adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila salah satu, sebagian atau semua inputnya berlogika 1.

Gerbang NAND

NAND akan menghasilkan output berlogika 0 apabila semua inputnya berlogika 1 dan sebaliknya output berlogika 1 apabila salah satu, sebagian atau semua inputnya berlogika 0.

Gerbang NOR

NOR adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila salah satu, sebagian atau semua inputnya berlogika 1 dan sebaliknya output berlogika 1 apabila semua inputnya berlogika 0.

4. Percobaan

[Daftar]

4.1 Prosedur Percobaan

[Daftar]

1. Siapkan semua alat dan bahan.

2. Susun logicstate, gerbang AND, gerbang OR, gerbang NOR, gerbang NAND, dan logicprobe sesuai gambar rangkaian.

3. Hubungkan semua pin sesuai gambar rangkaian.

4. Jalankan simulasi. Aktifkan logicstate secara bergantian sesuai tabel kebenaran untuk mengtahui logika output gerbang.

2. Susun logicstate, gerbang AND, gerbang OR, gerbang NOR, gerbang NAND, dan logicprobe sesuai gambar rangkaian.

3. Hubungkan semua pin sesuai gambar rangkaian.

4. Jalankan simulasi. Aktifkan logicstate secara bergantian sesuai tabel kebenaran untuk mengtahui logika output gerbang.

4.2 Rangkaian Simulasi

[Daftar]

1. two-wide, two-input AND-OR-INVERT gate

Pada gerbang AND, jika salah satu, sebagian, atau semua input yang berupa logicstate berlogika 0 maka output dari gerbang AND akan berlogika 0. Sebaliknya apabila semua input berlogika 1 maka output dari gerbang AND akan berlogika 1. Output dari gerbang AND kemudian mengalirkan arus ke input gerbang NOR. Pada gerbang NOR, jika salah satu, sebagian, atau semua input gerbang NOR berlogika 1 maka output dari gerbang NOR akan berlogika 0. Sebaliknya apabila semua input gerbang NOR berlogika 0 maka output dari gerbang NOR akan berlogika 1.

2. two-wide, two-input OR-AND-INVERT gate

Pada gerbang OR, jika semua input yang berupa logicstate berlogika 0 maka output dari gerbang OR akan berlogika 0, dan sebaliknya maka output gerbang OR akan berlogika 1. Kemudian output dari gerbang OR mengalirkan arus ke input gerbang NAND. Pada gerbang NAND, jika semua input gerbang NAND berlogika 1 maka output dari gerbang NAND akan berlogika 0. Sebaliknya jika salah satu, sebagian, atau semua input gerbang NAND berlogika 0, maka output dari gerbang NAND akan berlogika 1.

3. two-wide, four-input AND-OR-INVERT gate

Pada gerbang AND, jika salah satu, sebagian, atau semua input yang berupa logicstate berlogika 0 maka output dari gerbang AND akan berlogika 0. Sebaliknya apabila semua input berlogika 1 maka output dari gerbang AND akan berlogika 1. Output dari gerbang AND kemudian mengalirkan arus ke input gerbang NOR. Pada gerbang NOR, jika salah satu, sebagian, atau semua input gerbang NOR berlogika 1 maka output dari gerbang NOR akan berlogika 0. Sebaliknya apabila semua input gerbang NOR berlogika 0 maka output dari gerbang NOR akan berlogika 1.

4. four-wide, two-input AND-OR-INVERT gate

Pada gerbang AND, jika salah satu, sebagian, atau semua input yang berupa logicstate berlogika 0 maka output dari gerbang AND akan berlogika 0. Sebaliknya apabila semua input berlogika 1 maka output dari gerbang AND akan berlogika 1. Output dari gerbang AND kemudian mengalirkan arus ke input gerbang NOR. Pada gerbang NOR, jika salah satu, sebagian, atau semua input gerbang NOR berlogika 1 maka output dari gerbang NOR akan berlogika 0. Sebaliknya apabila semua input gerbang NOR berlogika 0 maka output dari gerbang NOR akan berlogika 1.

Pada gerbang AND, jika salah satu, sebagian, atau semua input yang berupa logicstate berlogika 0 maka output dari gerbang AND akan berlogika 0. Sebaliknya apabila semua input berlogika 1 maka output dari gerbang AND akan berlogika 1. Output dari gerbang AND kemudian mengalirkan arus ke input gerbang NOR. Pada gerbang NOR, jika salah satu, sebagian, atau semua input gerbang NOR berlogika 1 maka output dari gerbang NOR akan berlogika 0. Sebaliknya apabila semua input gerbang NOR berlogika 0 maka output dari gerbang NOR akan berlogika 1.

2. two-wide, two-input OR-AND-INVERT gate

Pada gerbang OR, jika semua input yang berupa logicstate berlogika 0 maka output dari gerbang OR akan berlogika 0, dan sebaliknya maka output gerbang OR akan berlogika 1. Kemudian output dari gerbang OR mengalirkan arus ke input gerbang NAND. Pada gerbang NAND, jika semua input gerbang NAND berlogika 1 maka output dari gerbang NAND akan berlogika 0. Sebaliknya jika salah satu, sebagian, atau semua input gerbang NAND berlogika 0, maka output dari gerbang NAND akan berlogika 1.

3. two-wide, four-input AND-OR-INVERT gate

Pada gerbang AND, jika salah satu, sebagian, atau semua input yang berupa logicstate berlogika 0 maka output dari gerbang AND akan berlogika 0. Sebaliknya apabila semua input berlogika 1 maka output dari gerbang AND akan berlogika 1. Output dari gerbang AND kemudian mengalirkan arus ke input gerbang NOR. Pada gerbang NOR, jika salah satu, sebagian, atau semua input gerbang NOR berlogika 1 maka output dari gerbang NOR akan berlogika 0. Sebaliknya apabila semua input gerbang NOR berlogika 0 maka output dari gerbang NOR akan berlogika 1.

4. four-wide, two-input AND-OR-INVERT gate

Pada gerbang AND, jika salah satu, sebagian, atau semua input yang berupa logicstate berlogika 0 maka output dari gerbang AND akan berlogika 0. Sebaliknya apabila semua input berlogika 1 maka output dari gerbang AND akan berlogika 1. Output dari gerbang AND kemudian mengalirkan arus ke input gerbang NOR. Pada gerbang NOR, jika salah satu, sebagian, atau semua input gerbang NOR berlogika 1 maka output dari gerbang NOR akan berlogika 0. Sebaliknya apabila semua input gerbang NOR berlogika 0 maka output dari gerbang NOR akan berlogika 1.

4.4 Download File

[Daftar]

Download materi HTML

Download file simulasi proteus two-wide, two-input AND-OR-INVERT gate

Download file simulasi proteus two-wide, two-input OR-AND-INVERT gate

Download file simulasi proteus two-wide, four-input AND-OR-INVERT gate

Download file simulasi proteus four-wide, two-input AND-OR-INVERT gate

Download video simulasi proteus

Download datasheet IC 4081 dan 4082

Download datasheet IC 4071

Download datasheet IC 4011

Download datasheet IC 4001 dan 4002

Download file simulasi proteus two-wide, two-input AND-OR-INVERT gate

Download file simulasi proteus two-wide, two-input OR-AND-INVERT gate

Download file simulasi proteus two-wide, four-input AND-OR-INVERT gate

Download file simulasi proteus four-wide, two-input AND-OR-INVERT gate

Download video simulasi proteus

Download datasheet IC 4081 dan 4082

Download datasheet IC 4071

Download datasheet IC 4011

Download datasheet IC 4001 dan 4002

5. Example 4.11

[Daftar]

7. Soal Pilihan Ganda

[Daftar]

1. Rangkaian AND-OR-INVERT berikut adalah...

a. two-wide, four-input AND-OR-INVERT gate

b. four-wide, two-input AND-OR-INVERT gate

c. eight-wide, two-input AND-OR-INVERT gate

d. two-wide, eight-input AND-OR-INVERT gate

2. Diantara rangkaian berikut yang merupakan four-wide, two-input AND-OR-INVERT gate adalah...

a.

b.

c.

d.

a. two-wide, four-input AND-OR-INVERT gate

b. four-wide, two-input AND-OR-INVERT gate

c. eight-wide, two-input AND-OR-INVERT gate

d. two-wide, eight-input AND-OR-INVERT gate

2. Diantara rangkaian berikut yang merupakan four-wide, two-input AND-OR-INVERT gate adalah...

a.

b.

c.

d.