5.3 Transistor Transistor Logic (TTL)

1. Tujuan

[Daftar]

1. Menjelaskan Transistor Transistor Logic (TTL).

2. Melakukan simulasi rangkaian Transistor Transistor Logic (TTL).

2. Melakukan simulasi rangkaian Transistor Transistor Logic (TTL).

2. Alat dan Bahan

[Daftar]

2.1 Alat

[Daftar]

2.2 Bahan

[Daftar]

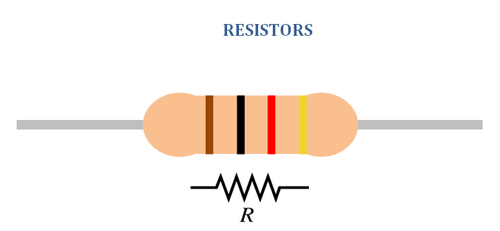

1. Resistor

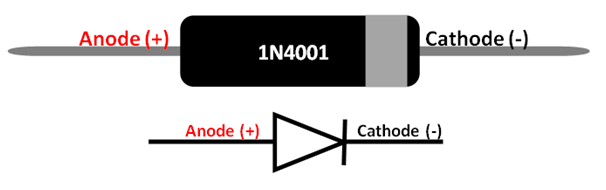

2. Dioda

3. Transistor NPN (BC547)

4. AND gate (IC 7010)

Resistor merupakan komponen pasif yang memiliki nilai resistansi tertentu dan berfungsi untuk menghambat jumlah arus listrik yang mengalir dalam suatu rangkaian.

Datasheet Resistor

Datasheet Resistor

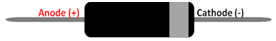

2. Dioda

Berfungsi untuk penyearah arus pada rangkaian.

Fitur Dioda Rectifier 1N4001:

1. Arus maju rata-rata 1A

2. Arus puncak non-repetitif 30A

3. Arus balik 5uA

4. Tegangan balik RMS 35V

5. Tegangan balik repetitif 50V

Fitur Dioda Schottky 10BQ040:

1. Arus maju rata-rata 1A

2. Tegangan drop 0.49V

3. Tegangan balik 40V

Fitur Dioda Varactor ZC830A:

1. Arus maju rata-rata 200mA

2. Tegangan balik breakdown 25V

3. Arus balik 0.2 - 10nA

4. Kapasitansi 10pF

Datasheet Dioda Rectifier 1N4001

Datasheet Dioda Schottky 10BQ040

Datasheet Dioda Varactor ZC830A

![]()

| Diode Type | Pinouts | Symbol |

|---|---|---|

| Rectifier Diode |  |

|

| Zener Diode |  |

|

| Schottky Diode |  |

|

Fitur Dioda Rectifier 1N4001:

1. Arus maju rata-rata 1A

2. Arus puncak non-repetitif 30A

3. Arus balik 5uA

4. Tegangan balik RMS 35V

5. Tegangan balik repetitif 50V

Fitur Dioda Schottky 10BQ040:

1. Arus maju rata-rata 1A

2. Tegangan drop 0.49V

3. Tegangan balik 40V

Fitur Dioda Varactor ZC830A:

1. Arus maju rata-rata 200mA

2. Tegangan balik breakdown 25V

3. Arus balik 0.2 - 10nA

4. Kapasitansi 10pF

Datasheet Dioda Rectifier 1N4001

Datasheet Dioda Schottky 10BQ040

Datasheet Dioda Varactor ZC830A

3. Transistor NPN (BC547)

Berfungsi sebagai penguat, sebagai sirkuit pemutus dan penyambung arus (switching), stabilisasi tegangan, dan modulasi sinyal.

Fitur:

1. DC Current gain(hfe) maksimal 800

2. Arus Collector kontinu(Ic) 100mA

3. Tegangan Base-Emitter(Vbe) 6V

4. Arus Base(Ib) maksimal 5mA

Datasheet Transistor BC548 dan BC547

Fitur:

1. DC Current gain(hfe) maksimal 800

2. Arus Collector kontinu(Ic) 100mA

3. Tegangan Base-Emitter(Vbe) 6V

4. Arus Base(Ib) maksimal 5mA

Datasheet Transistor BC548 dan BC547

4. AND gate (IC 7010)

AND adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila salah satu, sebagian atau semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila semua inputnya berlogika 1.

Konfigurasi Pin:

Datasheet IC 4071

Konfigurasi Pin:

| Pin Number | Pin Name | Description |

|---|---|---|

| 6, 8, 12 | Q1 & Q2 | Output gate 1, 2, dan 3 |

| 1, 2, 13 | A1 - D1 | Input gate 1 |

| 3, 4, 5 | A2 - D2 | Input gate 2 |

| 9, 10, 11 | A3 - D3 | Input gate 3 |

| 7 | GND | Ground |

| 14 | VDD | Input tegangan VDD |

Datasheet IC 4071

3. Dasar Teori

[Daftar]

Transistor Transistor Logic (TTL)

5.3.1 Standard TTL

5.3.11 Current Transient and Power Supply Decoupling

5.3.1 Standard TTL

5.3.1.1 Operasi Rangkaian

5.3.1.2 Totem-Pole Output Stage

5.3.1.Karakteristik

5.3.2 Other Logic Gates in Standard TTL5.3.1.2 Totem-Pole Output Stage

5.3.1.Karakteristik

VIL = 0.8 V; VIH = 2 V; IIH = 40 A; IIL = 1.6 mA; VOH = 2.4 V; VOL = 0.4 V; IOH = 400 A; IOL = 16 mA; VCC = 4.75–5.25 V (74-series) and 4.5–5.5 V (54-series); propagation delay (for a load resistance of 400 Ω, a load capacitance of 15 pF and an ambient temperature of 25 °C) = 22 ns (max.) for LOW-to-HIGH transition at the output and 15 ns (max.) for HIGHto-LOW output transition; worst-case noise margin = 0.4 V; fan-out = 10; ICCH (for all four gates) = 8 mA; ICCL (for all four gates) = 22 mA; operating temperature range = 0–70 °C (74- series) and −55 to +125 °C (54-series); speed–power product = 100 pJ; maximum flip-flop toggle frequency = 35 MHz.

5.3.2.1 NOT Gate

5.3.2.2 NOR Gate

5.3.2.3 AND Gate

5.3.2.4 OR Gate

5.3.2.5 EXCLUSIVE-OR Gate (X-OR)

5.3.2.6 AND-OR-INVERT Gate

5.3.2.7 Open Collector Gate

5.3.2.8 Tristate Gate

5.3.3 Low Power TTL5.3.2.2 NOR Gate

5.3.2.3 AND Gate

5.3.2.4 OR Gate

5.3.2.5 EXCLUSIVE-OR Gate (X-OR)

5.3.2.6 AND-OR-INVERT Gate

5.3.2.7 Open Collector Gate

5.3.2.8 Tristate Gate

5.3.3.1 Karakteristik

5.3.4 High Power TTL (74H/54H)

VIH = 2 V; VIL = 0.7 V; IIH = 10 A; IIL = 0.18 mA; VOH = 2.4 V; VOL = 0.4 V; IOH = 200 A; IOL = 3.6 mA; VCC = 4.75–5.25 V (74-series) and 4.5–5.5 V (54-series); propagation delay (for a load resistance of 4000 Ω, a load capacitance of 50 pF, VCC = 5 V and an ambient temperature of 25 °C) = 60 ns (max.) for both LOW-to-HIGH and HIGH-to-LOW output transitions; worst-case noise margin = 0.3 V; fan-out = 20; ICCH (for all four gates) = 0.8 mA; ICCL (for all four gates) = 2.04 mA; operating temperature range = 0–70 °C (74-series) and −55 to +125 °C (54-series); speed–power product = 33 pJ; maximum flip-flop toggle frequency = 3 MHz.

5.3.4.1 Karakteristik

5.3.5 Schottky TTL (74S/54S)

VIH = 2 V; VIL = 0.8 V; IIH = 50 A; IIL = 2 mA; VOH = 2.4 V; VOL = 0.4 V; IOH = 500 A; IOL = 20 mA; VCC = 4.75–5.25 V (74-series) and 4.5–5.5 V (54-series); propagation delay (for a load resistance of 280 Ω, a load capacitance of 25 pF, VCC = 5 V and an ambient temperature of 25 °C) = 10 ns (max.) for both LOW-to-HIGH and HIGH-to-LOW output transitions; worst–case noise margin = 0.4 V; fan-out = 10; ICCH (for all four gates) = 16.8 mA; ICCL (for all four gates) = 40 mA; operating temperature range = 0–70 °C (74-series) and −55 to +125 °C (54-series); speed–power product = 132 pJ; maximum flip-flop frequency = 50 MHz.

5.3.5.1 Karakteristik

5.3.6 Low Power Schottky TTL (74LS/54LS)

VIH = 2 V; VIL = 0.8 V; IIH = 50 A; IIL = 2 mA; VOH = 2.7 V; VOL = 0.5 V; IOH = 1 mA; IOL = 20 mA; VCC = 4.75–5.25 V (74-series) and4.5–5.5 V (54-series); propagation delay (for a load resistance of 280 Ω, a load capacitance of 15 pF,VCC = 5 V and an ambient temperature of 25 °C) = 5 ns (max.) for LOW-to-HIGH and 4.5 ns (max.)for HIGH-to-LOW output transitions; worst-case noise margin = 0.3 V; fan-out = 10; ICCH (for allfour gates) = 16 mA; ICCL (for all four gates) = 36 mA; operating temperature range = 0–70 °C (74-series) and −55 to +125 °C (54-series); speed–power product = 57 pJ; maximum flip-flop toggle frequency = 125 MHz.

5.3.6.1 Karakteristik

5.3.7 Advance Low-Power Schottky TTL (74ALS/54ALS)

VIH = 2 V; VIL = 0.8 V; IIH = 20A; IIL = 0.4 mA; VOH = 2.7 V; VOL = 0.5 V; IOH = 0.4 mA; IOL = 8 mA; VCC = 4.75–5.25 V (74-series) and 4.5–5.5 V (54-series); propagation delay (for a load resistance of 280 Ω, a load capacitance of 15 pF, VCC = 5 V and an ambient temperature of 25 °C) = 15 ns (max.) for both LOW-to-HIGH and HIGH-to-LOW output transitions; worst-case noise margin = 0.3 V; fan-out = 20; ICCH (for all four gates) = 1.6 mA; ICCL (for all four gates) = 4.4 mA; operating temperature range = 0–70 °C (74-series) and −55 to +125 °C (54-series); speed–power product = 18 pJ; maximum flip-flop toggle frequency = 45 MHz.

5.3.7.1 Karakteristik

5.3.8 Advance Schottky TTL (74AS/54AS)

VIH = 2 V; VIL = 0.8 V; IIH = 20 A; IIL = 0.1 mA; VOH = (VCC −2) V; VOL = 0.5 V; IOH = 0.4 mA; IOL = 8 mA (74ALS) and 4 mA (54ALS); VCC = 4.5–5.5 V; propagation delay (for a load resistance of 500 Ω, a load capacitance of 50 pF, VCC = 4.5–5.5 V and an ambient temperature of minimum to maximum) = 11 ns/16 ns (max.) for LOW-to-HIGH and 8 ns/13 ns for HIGH-to-LOW output transitions (74ALS/54ALS); worst-case noise margin = 0.3 V; fan-out = 20; ICCH (for all four gates) = 0.85 mA; ICCL (for all four gates) = 3 mA; operating temperature range = 0–70 °C (74-series) and −55 to +125 °C (54-series); speed–power product = 4.8 pJ; maximum flip-flop toggle frequency = 70 MHz.

5.3.8.1 Karakteristik

5.3.9 Fairchild Advance Schottky TTL (74F/54F)

VIH = 2 V; VIL = 0.8 V; IIH = 20 A; IIL = 0.5 mA; VOH = (VCC−2) V; VOL = 0.5 V; IOH = 2 mA; IOL = 20 mA; VCC = 4.5–5.5 V; propagation delay (for a load resistance of 50 Ω, a load capacitance of 50 pF, VCC = 4.5–5.5 V and an ambient temperature of minimum to maximum) = 4.5 ns/5 ns (max.) for LOW-to-HIGH and 4 ns/5 ns (max.) for HIGH-to-LOW output transitions (74AS/54AS); worst-case noise margin = 0.3 V; fan-out = 40; ICCH (for all four gates) = 3.2 mA; ICCL (for all four gates) = 17.4 mA; operating temperature range = 0–70 °C (74-series) and −55 to +125 °C (54-series); speed–power product = 13.6 pJ; maximum flip-flop toggle frequency = 200 MHz.

5.3.9.1 Karakteristik

5.3.10 Floating and Unused Inputs

VIH = 2 V; VIL = 0.8 V; IIH = 20 A; IIL = 0.6 mA; VOH = 2.7 V; VOL = 0.5 V; IOH = 1 mA; IOL = 20 mA; VCC = 4.75–5.25 V (74F) and 4.5– 5.5 V (54F); propagation delay (a load resistance of 500 Ω, a load capacitance of 50 pF and full operating voltage and temperature ranges) = 5.3 ns/7 ns (max.) for LOW-to-HIGH and 6 ns/6.5 ns (max.) for HIGH-to-LOW output transitions (74AS/54AS); worst-case noise margin = 0.3 V; fanout = 40; ICCH (for all four gates) = 2.8 mA; ICCL (for all four gates) = 10.2 mA; operating temperature range = 0–70 °C (74F-series) and −55 to +125 °C (54F-series); speed–power product = 10 pJ; maximum flip-flop toggle frequency = 125 MHz.

5.3.11 Current Transient and Power Supply Decoupling

4. Percobaan

[Daftar]

4.1 Prosedur Percobaan

[Daftar]

1. Siapkan semua alat dan bahan.

2. Susun alat dan bahan sesuai gambar rangkaian.

3. Hubungkan semua pin sesuai gambar rangkaian.

4. Jalankan simulasi. Aktifkan logicstate secara bergantian sesuai tabel kebenaran untuk mengetahui logika output gerbang.

2. Susun alat dan bahan sesuai gambar rangkaian.

3. Hubungkan semua pin sesuai gambar rangkaian.

4. Jalankan simulasi. Aktifkan logicstate secara bergantian sesuai tabel kebenaran untuk mengetahui logika output gerbang.

4.2 Rangkaian Simulasi

[Daftar]

5.6 Standard TTL NAND Gate

5.7 Current sinking and sourcing

5.8 Standard TTL INVERTER

5.9 Standard TTL NOR Gate

5.10 Standard TTL AND Gate

5.11 Standard TTL OR Gate

5.12 Standard TTL XOR Gate

5.13 Standard TTL 2-2 AOI Gate

5.14 Standard TTL NAND with Open Collector

5.15 Totem-Pole Tied Output Gates

5.16 Standard TTL Tristate Inverter

5.17 Low-Power TTL NAND Gate

5.18 High-Power TTL NAND Gate

5.19 Schottky TTL NAND Gate

5.20 Low-Power Schottky TTL NAND Gate

5.21 Advanced Low-Power Schottky TTL NAND Gate

5.22 Advanced Schottky TTL NAND Gate

5.23 Fairchild Advanced Schottky TTL NAND Gate

5.24 Handling unused input of AND and NAND Gate

5.25 Handling unused input of OR and NOR Gate

5.26 Input loading in the case of HIGH tied inputs of NAND and AND Gate

5.27 Input loading in the case of LOW tied inputs of NAND and AND Gate

5.28 Input loading in the case of tied inputs of NOR and OR Gate

5.29 Current Transient and Power Supply Decoupling

4.4 Download File

[Daftar]

Download materi HTML

Download file simulasi proteus 5.6

Download file simulasi proteus 5.8

Download file simulasi proteus 5.9

Download file simulasi proteus 5.10

Download file simulasi proteus 5.11

Download file simulasi proteus 5.12

Download file simulasi proteus 5.13

Download file simulasi proteus 5.14

Download file simulasi proteus 5.16

Download file simulasi proteus 5.17

Download file simulasi proteus 5.18

Download file simulasi proteus 5.19

Download file simulasi proteus 5.20

Download file simulasi proteus 5.21

Download file simulasi proteus 5.22

Download file simulasi proteus 5.23

Download file simulasi proteus 5.24-25

Download file simulasi proteus 5.26-28

Download video simulasi proteus

Download Datasheet Resistor

Download Datasheet Dioda Rectifier 1N4001

Download Datasheet Dioda Schottky 10BQ040

Download Datasheet Dioda Varactor ZC830A

Download Datasheet Transistor BC547

Download datasheet IC 7410 NAND

Download datasheet IC 7411 AND

Download datasheet IC 74HC4075 OR

Download datasheet IC 7427 NOR

Download file simulasi proteus 5.6

Download file simulasi proteus 5.8

Download file simulasi proteus 5.9

Download file simulasi proteus 5.10

Download file simulasi proteus 5.11

Download file simulasi proteus 5.12

Download file simulasi proteus 5.13

Download file simulasi proteus 5.14

Download file simulasi proteus 5.16

Download file simulasi proteus 5.17

Download file simulasi proteus 5.18

Download file simulasi proteus 5.19

Download file simulasi proteus 5.20

Download file simulasi proteus 5.21

Download file simulasi proteus 5.22

Download file simulasi proteus 5.23

Download file simulasi proteus 5.24-25

Download file simulasi proteus 5.26-28

Download video simulasi proteus

Download Datasheet Resistor

Download Datasheet Dioda Rectifier 1N4001

Download Datasheet Dioda Schottky 10BQ040

Download Datasheet Dioda Varactor ZC830A

Download Datasheet Transistor BC547

Download datasheet IC 7410 NAND

Download datasheet IC 7411 AND

Download datasheet IC 74HC4075 OR

Download datasheet IC 7427 NOR

5. Example

[Daftar]

1. Berdasarkan Gambar 5.30. Tentukan arus yang bersumber dari gerbang 1 ketika outputnya HIGH dan turun ketika outputnya LOW. Semua gerbang berasal dari keluarga TTL standar, dengan IIH = 40uA dan IIL = 1,6mA.

Solultion:

2. Berdasarkan diagram logika pada Gambar 5.31. Gerbang 1 dan gerbang 4 termasuk dalam keluarga TTL standar, sedangkan gerbang 2 dan gerbang 3 masing-masing milik keluarga Schottky TTL dan keluarga Schottky TTL berdaya rendah. Tentukan apakah kapabilitas fan-out gerbang 1 terlampaui. Data yang relevan untuk tiga keluarga logika diberikan pada Tabel 5.1.

Solution:

Solultion:

- Ketika outputnya TINGGI, input dari semua gerbang menarik arus satu per satu.

- Oleh karena itu, faktor pembebanan input = ekuivalen dengan input tujuh gerbang = 7 × 40 A = 280 A.

- Arus yang bersumber dari output gerbang 1 = 280 A.

- Ketika outputnya RENDAH, input korsleting gerbang AND dan gerbang NAND menawarkan beban yang sama dengan input tunggal karena transistor multi-emitor pada input gerbang. Input gerbang OR dan NOR menarik arus secara individual karena penggunaan transistor terpisah pada input gerbang.

- Oleh karena itu, faktor pembebanan input = ekuivalen dengan input lima gerbang = 5 × 1,6 = 8 mA.

- Arus yang ditenggelamkan oleh gerbang 1 keluaran = 8 mA.

2. Berdasarkan diagram logika pada Gambar 5.31. Gerbang 1 dan gerbang 4 termasuk dalam keluarga TTL standar, sedangkan gerbang 2 dan gerbang 3 masing-masing milik keluarga Schottky TTL dan keluarga Schottky TTL berdaya rendah. Tentukan apakah kapabilitas fan-out gerbang 1 terlampaui. Data yang relevan untuk tiga keluarga logika diberikan pada Tabel 5.1.

Solution:

- Saat input HIGH

- kemampuan sumber keluaran gerbang 1 = 400 A;

- persyaratan input gerbang 2 = 50 × 4 = 200 A;

- persyaratan input gerbang 3 = 20 × 2 = 40 A;

- persyaratan input gerbang 4 = 40 × 4 = 160 A;

- total kebutuhan arus input = 400 A;

- oleh karena itu, fan-out tidak terlampaui dalam status TINGGI.

- Saat input LOW

- kemampuan tenggelam keluaran gerbang 1 = 16 mA;

- persyaratan tenggelamnya gerbang 2 input = 2 mA;

- persyaratan tenggelamnya masukan gerbang 3 = 0,4 × 2 = 0,8 mA;

- persyaratan tenggelamnya gerbang 4 input = 1,6 mA;

- total kebutuhan arus input = 4,4 mA;

- karena keluaran dari gerbang 1 memiliki kemampuan penurunan arus sebesar 16 mA, kemampuan kipas keluar juga tidak terlampaui dalam keadaan RENDAH.

6. Problem

[Daftar]

1. Berdasarkan diagram logika pada Gambar 5.66. Tentukan arus yang bersumber dari gerbang NAND ketika outputnya TINGGI dan juga arus yang turun ketika outputnya RENDAH, diketahui bahwa IIH (gerbang AND) = 0,02 mA, IIL (gerbang AND) = 0,4 mA, IIH (OR gerbang) = 0,04 mA, IIL (gerbang OR) = 1,6 mA, IOH (gerbang NAND) = 1,0 mA, IOL (gerbang NAND) = 20,0 mA.

Solution:

Arus HIGH = 2*IIH(AND) + IIH(OR) = 0.04 + 0.04 = 0.08mA

Arus LOW = IIL(AND) + IIL(OR) = 0.4 + 1.6 = 2.0mA

2. Berapa banyak input dari Low-Power Schottky TTL NAND yang dapat digerakkan secara andal dari satu output dari Schottky TTL NAND, diketahui spesifikasi relevan berikut untuk perangkat dari dua subfamili TTL:

Schottky TTL: IOH = 1,0 mA; IIH = 0,05 mA; IOL = 20,0 mA; IIL = 2.0 mA

Low-Power Schottky TTL: IOH = 0.4 mA; IIH = 0,02 mA; IOL = 8,0 mA; IIL = 0,4 mA

Solution:

Fan-out HIGH = 1mA/0.02mA = 50

Fan-out LOW = 20mA/0.4mA = 50

Hasil akhir = 50

Solution:

Arus HIGH = 2*IIH(AND) + IIH(OR) = 0.04 + 0.04 = 0.08mA

Arus LOW = IIL(AND) + IIL(OR) = 0.4 + 1.6 = 2.0mA

2. Berapa banyak input dari Low-Power Schottky TTL NAND yang dapat digerakkan secara andal dari satu output dari Schottky TTL NAND, diketahui spesifikasi relevan berikut untuk perangkat dari dua subfamili TTL:

Schottky TTL: IOH = 1,0 mA; IIH = 0,05 mA; IOL = 20,0 mA; IIL = 2.0 mA

Low-Power Schottky TTL: IOH = 0.4 mA; IIH = 0,02 mA; IOL = 8,0 mA; IIL = 0,4 mA

Solution:

Fan-out HIGH = 1mA/0.02mA = 50

Fan-out LOW = 20mA/0.4mA = 50

Hasil akhir = 50

7. Soal Pilihan Ganda

[Daftar]

1. Berdasarkan rangkaian berikut, apabila kedua input (logicstate) berlogika 1 pernyataan di bawah ini yang benar adalah...

a. Output berlogika 0 dan Q3 aktif.

b. Output berlogika 1 dan Q3 aktif

c. Output berlogika 0 dan Q3 tidak aktif

d. Output berlogika 1 dan Q3 tidak aktif

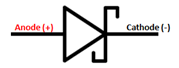

2. Gerbang yang ditunjukkan oleh gambar berikut adalah...

a. AND

b. OR

c. NAND

d. NOT

a. Output berlogika 0 dan Q3 aktif.

b. Output berlogika 1 dan Q3 aktif

c. Output berlogika 0 dan Q3 tidak aktif

d. Output berlogika 1 dan Q3 tidak aktif

2. Gerbang yang ditunjukkan oleh gambar berikut adalah...

a. AND

b. OR

c. NAND

d. NOT